-

タグ

タグ

- アーキテクト

- アジャイル開発

- アプリ開発

- インシデントレスポンス

- イベントレポート

- カスタマーストーリー

- カルチャー

- 官民学・業界連携

- 企業市民活動

- クラウド

- クラウドインテグレーション

- クラブ活動

- コーポレート

- 広報・マーケティング

- 攻撃者グループ

- 子育て、生活

- サイバー救急センター

- サイバー救急センターレポート

- サイバー攻撃

- サイバー犯罪

- サイバー・グリッド・ジャパン

- サプライチェーンリスク

- システム開発

- 趣味

- 障がい者採用

- 初心者向け

- 白浜シンポジウム

- 情シス向け

- 情報モラル

- 情報漏えい対策

- 人材開発・教育

- 診断30周年

- スレットインテリジェンス

- すごうで

- セキュリティ

- セキュリティ診断

- セキュリティ診断レポート

- 脆弱性

- 脆弱性管理

- ゼロトラスト

- 対談

- ダイバーシティ

- テレワーク

- データベース

- デジタルアイデンティティ

- 働き方改革

- 標的型攻撃

- プラス・セキュリティ人材

- モバイルアプリ

- ライター紹介

- ラックセキュリティアカデミー

- ランサムウェア

- リモートデスクトップ

- 1on1

- AI

- ASM

- CIS Controls

- CODE BLUE

- CTF

- CYBER GRID JOURNAL

- CYBER GRID VIEW

- DevSecOps

- DX

- EC

- EDR

- FalconNest

- IoT

- IR

- JSOC

- JSOC INSIGHT

- LAC Security Insight

- NDR

- OWASP

- SASE

- Tech Crawling

- XDR

半導体チップの設計やそれを利用した機器の設計手法は平成になってから大きく進歩してきました。初期の頃は自社内に全ての設計部門と製造部門が存在し、それにより安定した品質の高い製品を世の中に送り出していました。

しかし、昨今は設計に利用する開発ツールが進化し、より便利な機能を今まで考えられなかった手法で実現できるようになってきました。自社外の設計・製造に従事する技術者を活用することで、設計・製造に関するコストを下げ低価格で良い製品を世の中に送り出しています。一方、設計・製造のノウハウが流出し模造品が多く流通してしまったり、スパイ活動などに利用されたりすることが問題となっています。

ここでは産学官連携による、設計・製造におけるチップの脆弱性の検知技術[1]についてお話したいと思います。

ハードウエアセキュリティと脆弱性

情報セキュリティでは、機密性(Confidentiality)、完全性(Integrity)、可用性(Availability)に影響がでるようなものを一般に脆弱性と呼んでいます。多くの原因はソフトウエアです。機器を組み合わせたときに発生するものも、やはりソフトウエアが原因となります。では、ハードウエアが原因となるような脆弱性はないのでしょうか。

ハードウエアの脆弱性を調べると、CPUの投機的実行によってサイドチャネルで実行中のプログラムのデータを観測できるというものがあります。これは、CPUを高速化し機能を追加していくことで、投機的実行によるデータの漏えいを観測出来るというものです。ただし、脆弱性として発見されたときと同じハードウエア/ソフトウエアの構成でないと再現できないため、身近な脅威として認識されていないケースが多いです。また、CPUベンダによるパッチである程度防げているという現実もあります。

では、これ以外に機密性、完全性、可用性を侵害するようなハードウエアはあるのでしょうか。この点について少し掘り下げてみましょう。

脆弱性を引き起こすハードウエアとは

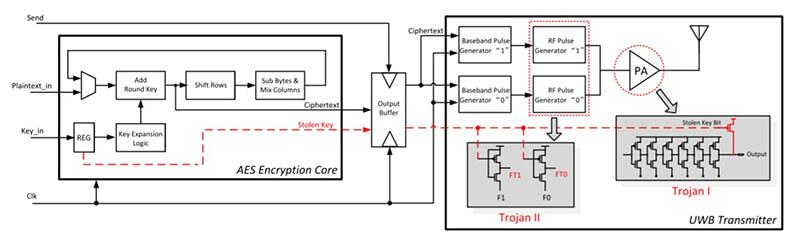

脆弱性の原因となるハードウエアというものを実例とともに紹介します。まず、チップそのものの内部に漏えいさせる機能を新たに追加したものです(図1)。これは、チップを作るときに利用するウエハーと呼ばれる素材の上に電子回路を組み込んだものです。ただ、これは研究として実験的に試みたものであり、ここまでのことをするには高度な知識と技術が必要となります[2]。

「Silicon Demonstration of Hardware Trojan Design and Detection in Wireless Cryptographic ICs(http://jin.ece.ufl.edu/papers/TVLSI16.pdf)」より図の引用

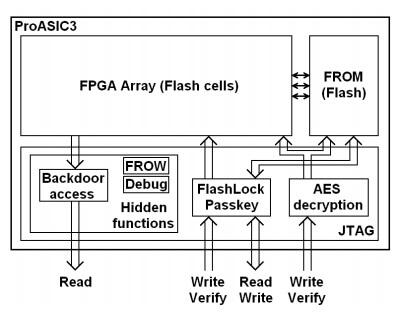

次にFPGAチップ内にバックドアと呼ばれる機能を追加し外部から遠隔操作や情報の搾取を行うものです(図2)。これは設計時にFPGAのロジックにそのような機能モジュールを追加しておくことで可能となります。設計時に判明しなかったのかという疑問はあるかと思います。しかし設計工程が複雑になり、工程の全てを見ることが出来なければ、このような機能モジュールが組み込まれる事は見逃されてしまいます[3]。

「Breakthrough silicon scanning discovers backdoor in military chip」より図の引用

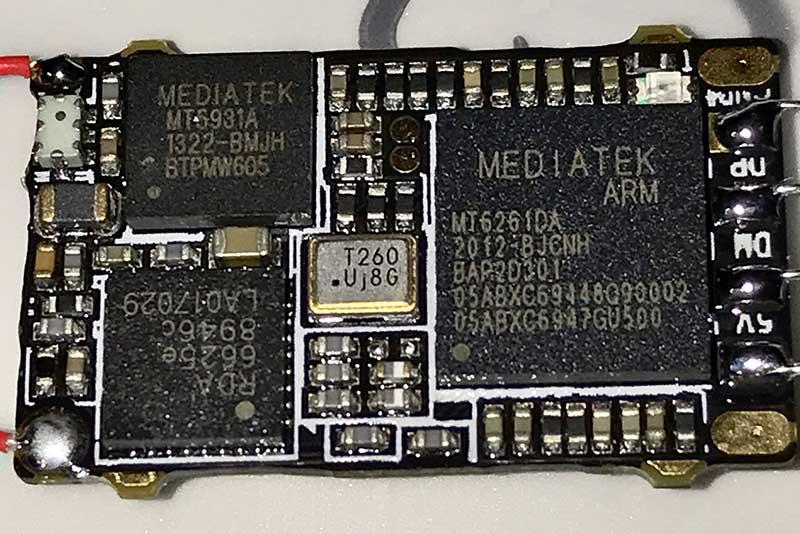

最後に、諜報用のモジュールを実際の製品の中に忍ばせてしまうケースです。このモジュールは大人の親指サイズ程度の面積で実現され、半導体そのものとプリント基板そしてコネクタの高さを足した薄さで実現されています[4](図3)。

脆弱性を引き起こすハードウエアを検知する際の課題

このような不正なものは、どうすれば排除できるでしょうか。できることなら、市場に出る前に非破壊で検査し、脆弱性を引き起こすようなハードウエアが使われていないかを確認するのが最も理想的です。また、ゲートアレイの設計時に設計情報から不正なハードウエア記述を見つける事ができるのが望ましいです。

非破壊で基板上の電子部品を追跡する仕組みとして、JTAG(IEEE1149.1)と呼ばれるテスト機能があります。しかし、EID(Electrical IDentification)まで偽装された場合には追跡は出来なくなります。では、そういった場合はどうすれば良いでしょうか。

解決手法

チップであれば、半導体でウエハーに書き込まれる前にRTL(Register Transfer Level)を検査すれば判ります。ところが、このRTLで記述される分量が数十万ゲートから数百万ゲートという単位に膨れ上がると人間では検査できません。またRTLを半導体に書き込む形式に変換する合成ツールでも判別は不可能です。

しかし、RTL内には何らかの特徴があるはずです。そこで、RTLの情報をインプットとしてAIによる識別を行い、ハードウエア脆弱性であるハードウエアトロイを見つけます。AIには悪性のハードウエアトロイの情報だけを学習させ、RTL中のハードウエアトロイの検知を行わせます。

では、完成された製品の脆弱性の検知はどうするかという課題の解決はどうすべきでしょうか。我々が通常利用しているパソコンは、EDR(Endpoint Detection and Response)と呼ばれるソフトウエアによってオンラインで接続されていれば100%に近い脆弱性を招くマルウエアの検知が可能です。しかし、電子機器にEDRを載せるのは困難です。なぜなら、元々、電子機器は限られたCPUの計算量とメモリしかないからです。

どうしたものかと困っていた時、電子機器の外部から観測される電力が電子機器の動作によって変化する事を実験で知りました。非常に微量な変化ですが、電子機器内のプログラムの変化に応じて、その電力がわずかに変動するのです。現在、この変動を計測しAIで学習させ異常を検知することが可能なのかという点について、日夜研究を進めている段階です。

さいごに

ラックは令和元年に、内閣府―官民研究開発投資拡大プログラム(PRISM)のひとつである革新的AIネットワーク統合基盤技術の研究開発として、「設計・製造におけるチップの脆弱性検知手法の研究開発」に取り組みました。また、ほぼ同時期にハードウエアセキュリティについても、早稲田大学 理工学術院総合研究所との産学連携をしています。

今後も、企業や学校法人と連携をしてAIを活用したハードウエアセキュリティの研究開発を進め、いずれ社会実装として日本のみならず世界各国の設計・製造工程に利用されるようにして行きたいと考えています。

参考文献

- [1] 早稲田大学,KDDI総合研究所,ラック:設計・製造におけるチップ脆弱性検知手法の研究開発, 総務省, 2019,

https://www.soumu.go.jp/main_content/000700017.pdf - [2] Yu Liu et. al, "Silicon Demonstration of Hardware Trojan Design and Detection in Wireless Cryptographic ICs", IEEE Transactions on Very Large Scale Integration (VLSI) Systems ( Volume: 25, Issue: 4 , April 2017 ) pp.1506 - 1519

- [3] Sergei Skorobogatov, Chiristopher Woods: Breakthrough silicon scanning discovers backdoor in military chip, Cryptographic Hardware and Embedded Systems Workshop (CHES 2012), 9-12 September 2012

- [4] 中国で盗聴器の仕込まれたモバイルバッテリーが騒動に, ZDNet Japan, 2021, https://japan.zdnet.com/article/35165719/

タグ

- アーキテクト

- アジャイル開発

- アプリ開発

- インシデントレスポンス

- イベントレポート

- カスタマーストーリー

- カルチャー

- 官民学・業界連携

- 企業市民活動

- クラウド

- クラウドインテグレーション

- クラブ活動

- コーポレート

- 広報・マーケティング

- 攻撃者グループ

- もっと見る +

- 子育て、生活

- サイバー救急センター

- サイバー救急センターレポート

- サイバー攻撃

- サイバー犯罪

- サイバー・グリッド・ジャパン

- サプライチェーンリスク

- システム開発

- 趣味

- 障がい者採用

- 初心者向け

- 白浜シンポジウム

- 情シス向け

- 情報モラル

- 情報漏えい対策

- 人材開発・教育

- 診断30周年

- スレットインテリジェンス

- すごうで

- セキュリティ

- セキュリティ診断

- セキュリティ診断レポート

- 脆弱性

- 脆弱性管理

- ゼロトラスト

- 対談

- ダイバーシティ

- テレワーク

- データベース

- デジタルアイデンティティ

- 働き方改革

- 標的型攻撃

- プラス・セキュリティ人材

- モバイルアプリ

- ライター紹介

- ラックセキュリティアカデミー

- ランサムウェア

- リモートデスクトップ

- 1on1

- AI

- ASM

- CIS Controls

- CODE BLUE

- CTF

- CYBER GRID JOURNAL

- CYBER GRID VIEW

- DevSecOps

- DX

- EC

- EDR

- FalconNest

- IoT

- IR

- JSOC

- JSOC INSIGHT

- LAC Security Insight

- NDR

- OWASP

- SASE

- Tech Crawling

- XDR